Hot Chips 2020 Live Blog: Xilinx Versal ACAPs (9:00am PT)

by Dr. Ian Cutress on August 18, 2020 12:00 PM EST

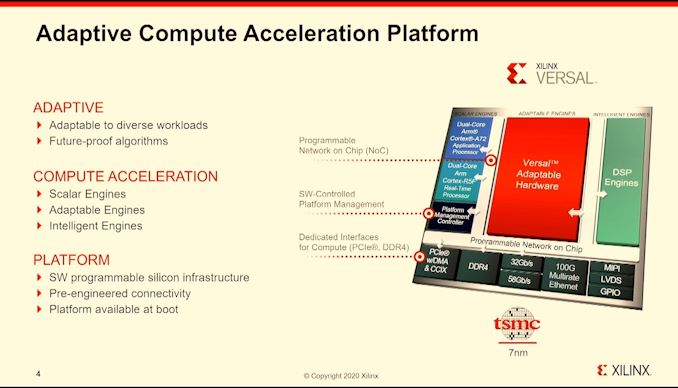

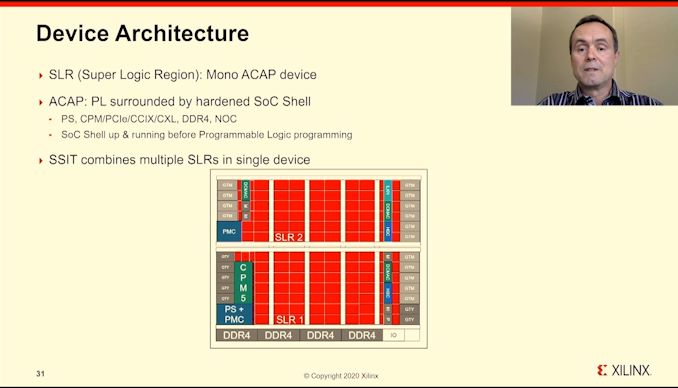

12:03PM EDT - ACAP = Adaptive Computing Acceleration Platform

12:04PM EDT - It's what Xilinx called its new FPGAs with lots of additional hardened controls

12:05PM EDT - Versal is the product family

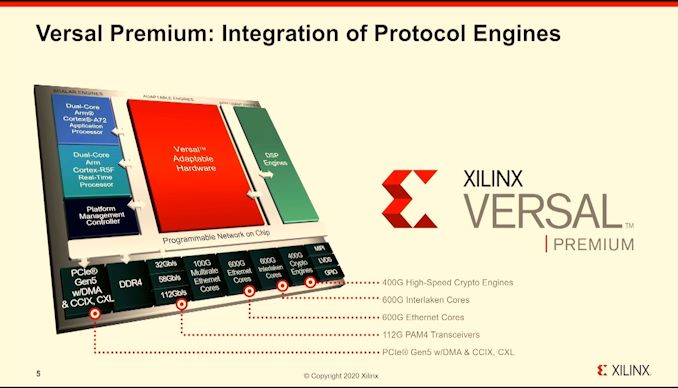

12:05PM EDT - Premium is the top end

12:05PM EDT - Versal is designed to be future proof

12:05PM EDT - Compute acceleration with multiple engines

12:05PM EDT - Scalar, Adaptable, Intelligent engines

12:05PM EDT - DSPs

12:06PM EDT - SW Programmable infrastructure

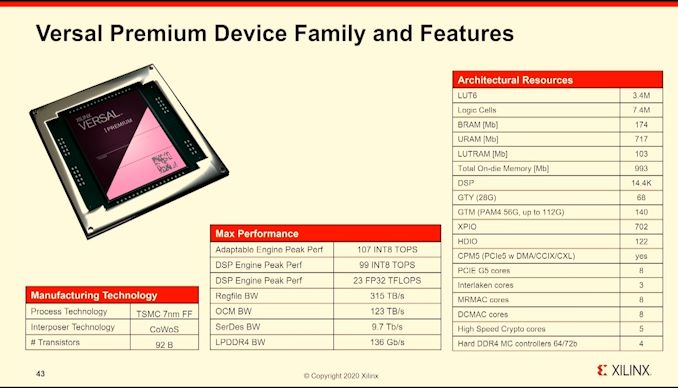

12:06PM EDT - Built on TSMC 7nm FF

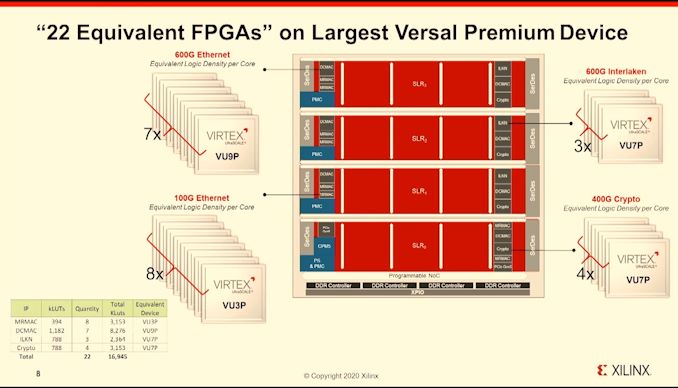

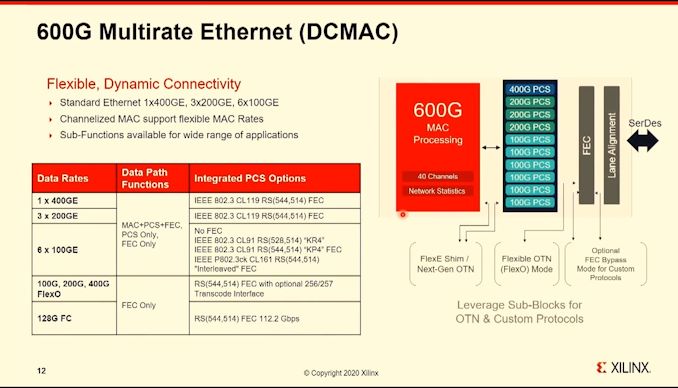

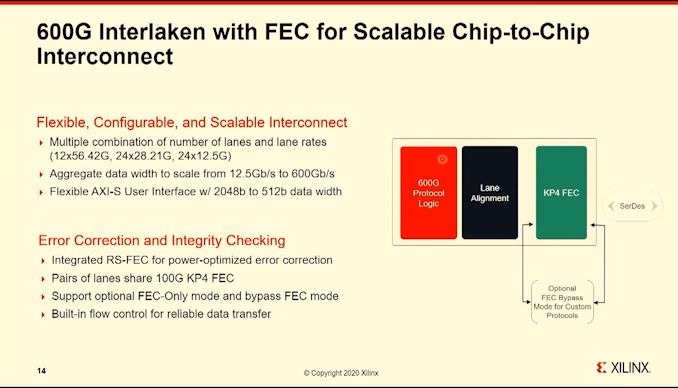

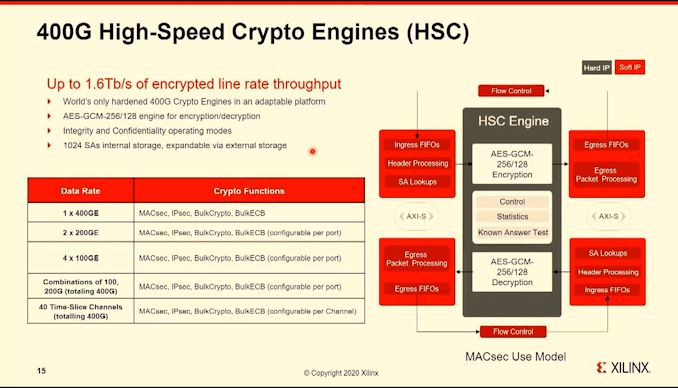

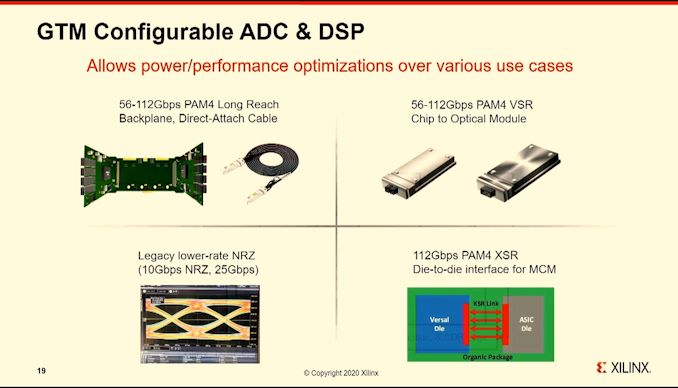

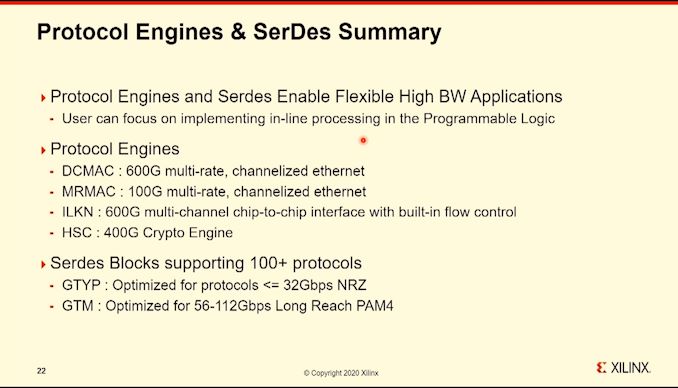

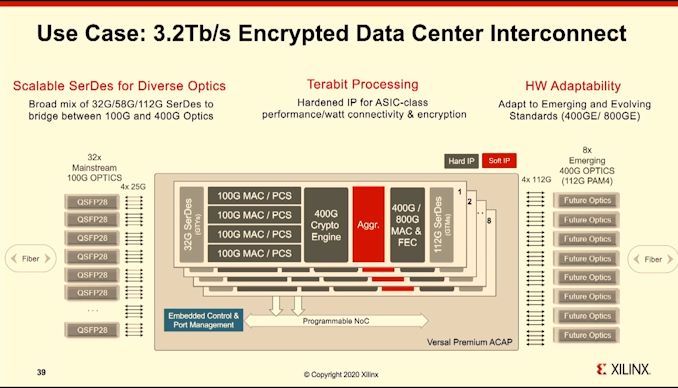

12:06PM EDT - 112G PAM4, 600G Ethernet Cores, 400G hardened Crypto engines

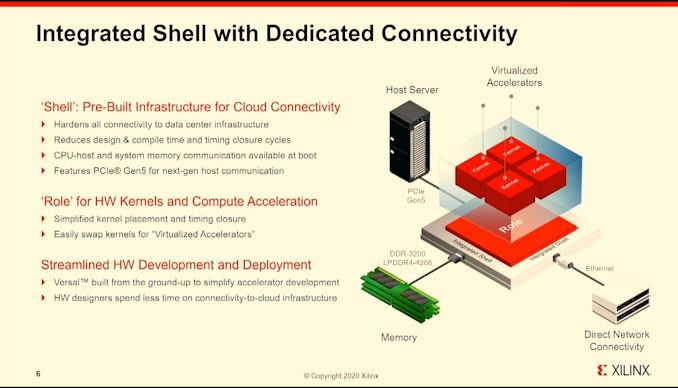

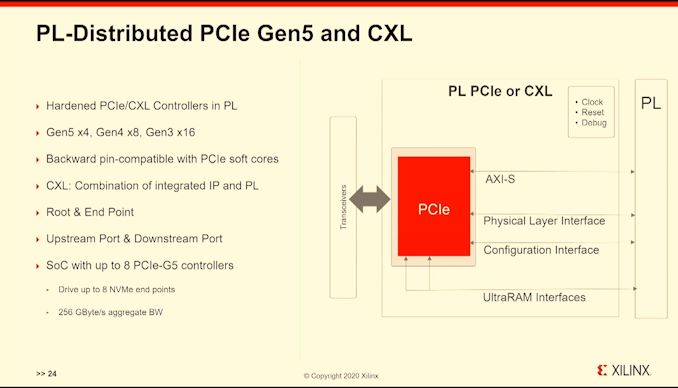

12:07PM EDT - Off-the-shelf connectivity, PCIe 5

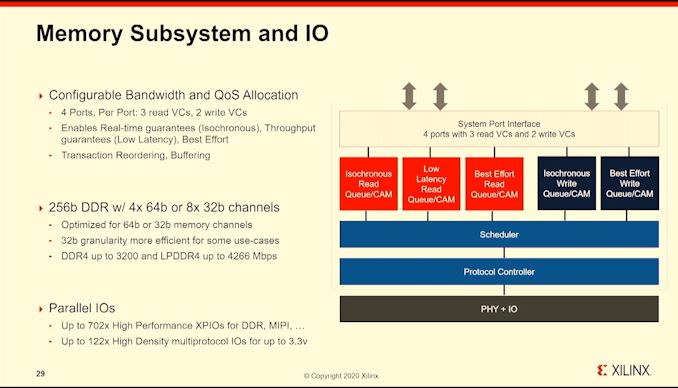

12:07PM EDT - DDR4-3200 / LPDDR4-4266

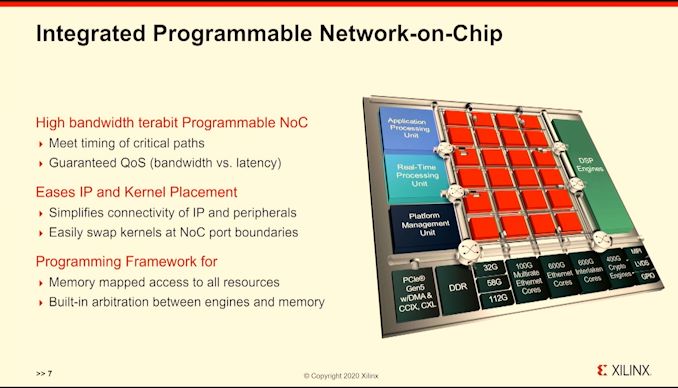

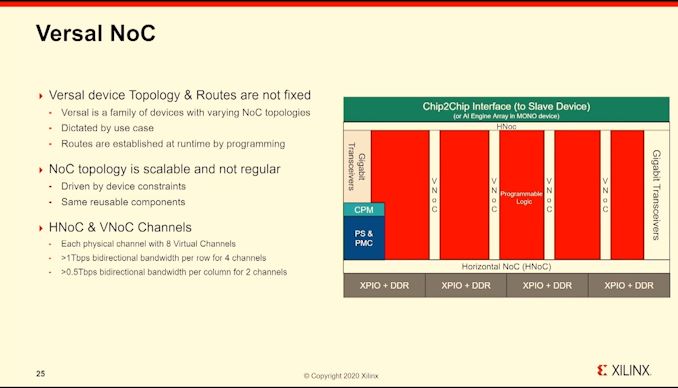

12:07PM EDT - High bandwidth network on chip

12:08PM EDT - Can prioritize between latency and bandwidth requirements

12:08PM EDT - Guaranteed QoS

12:08PM EDT - All resources can be memory mapped

12:08PM EDT - Built in arbitration

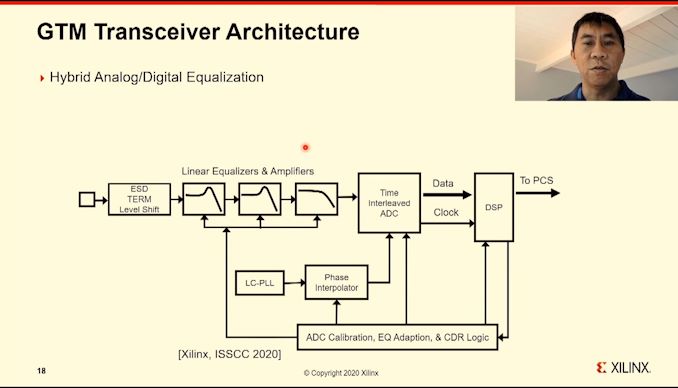

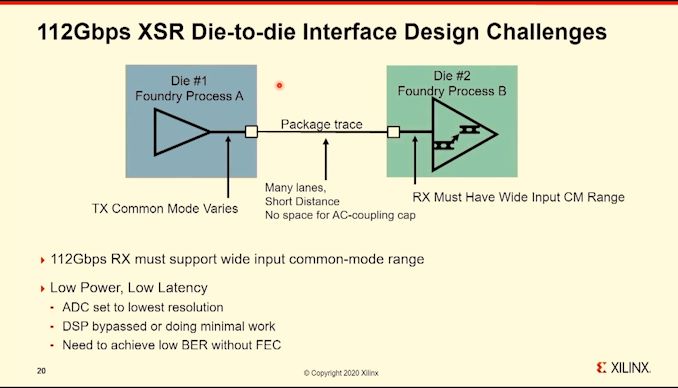

12:08PM EDT - 112G PAM4 with hardened IP to reduce logic requirements

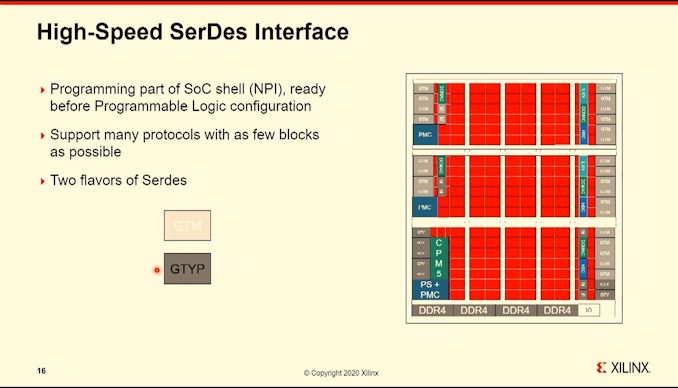

12:09PM EDT - Versal has 3 different types of memory slots - Memory controllers, Protocol Engines, Serdes

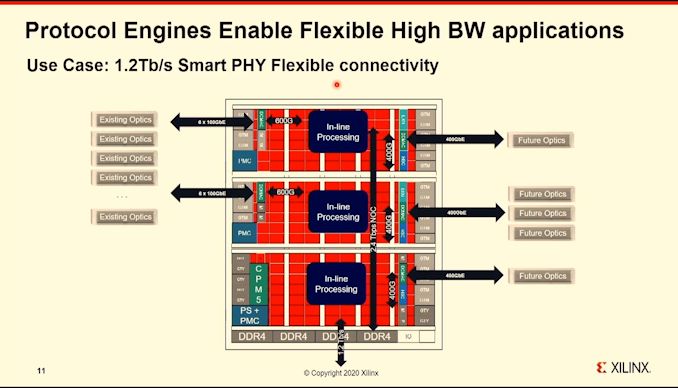

12:11PM EDT - Here's an example of a 1.2 Tb/s smart PHY creation using Versal Premium

12:11PM EDT - Focus effort on building custom logic for future standards

12:11PM EDT - Ports can be added wihtout using programmable logic due to the hardened IPs

12:12PM EDT - DCMAC: 600 GbE of ethernet with bifurcation at different rates

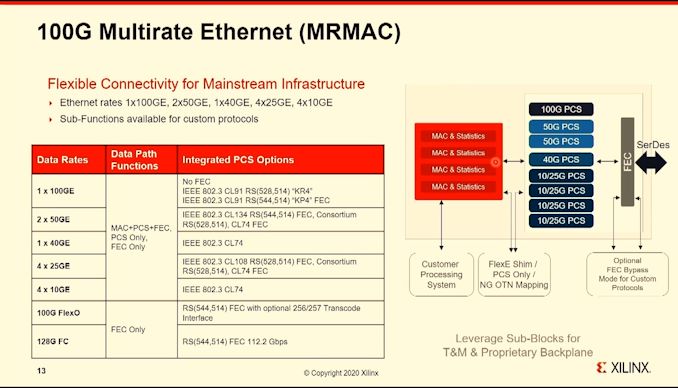

12:13PM EDT - MRMAC 100G Multi-rate Ethernet

12:14PM EDT - 400G High-Speed Crypto

12:14PM EDT - Encryption at line-read

12:14PM EDT - 40 channels

12:14PM EDT - AES-GCM 256/128

12:14PM EDT - Soft-IP around the hardened HSC Core

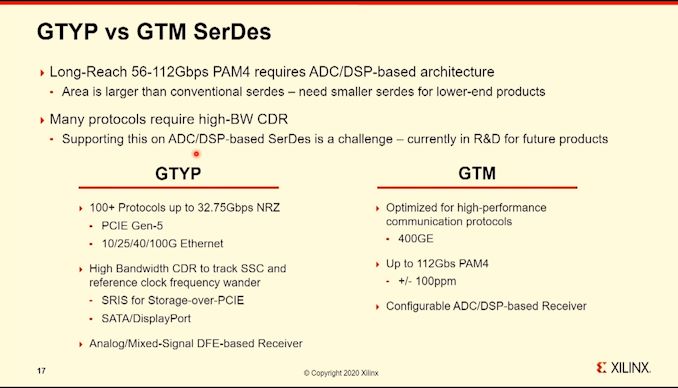

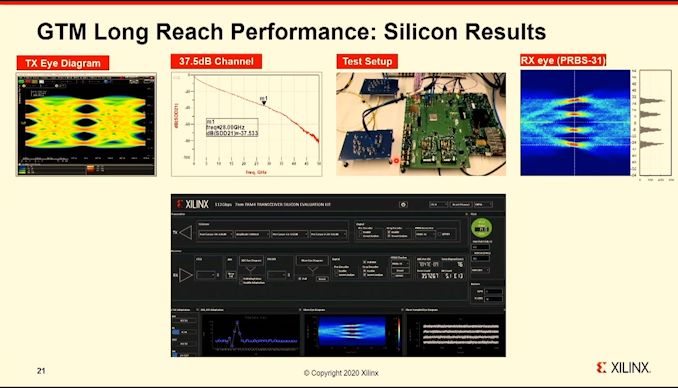

12:15PM EDT - Two flavors of Serdes

12:16PM EDT - 7nm is geared towards minimum-sized clock gates

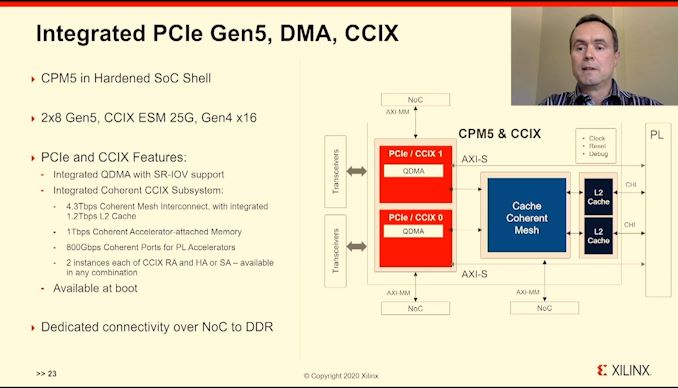

12:17PM EDT - Integrated PCIe G5, DMA, CCIX

12:17PM EDT - Block is available at boot

12:18PM EDT - x16 PCIe G5

12:18PM EDT - 8 NVMe end-points up to 256 GB/sec

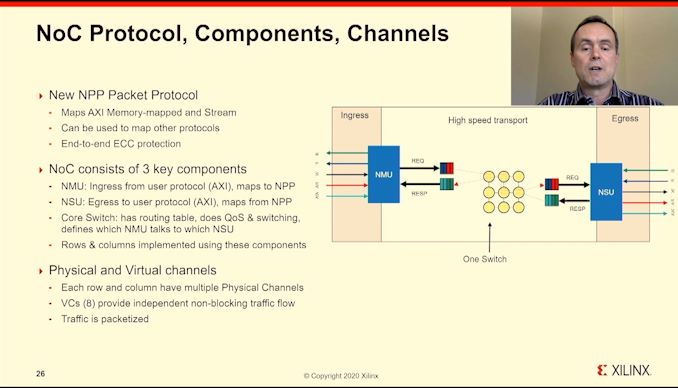

12:19PM EDT - NoC Packet Protocol - AXI Memory Mapping and Stream

12:19PM EDT - Traffic is packetized

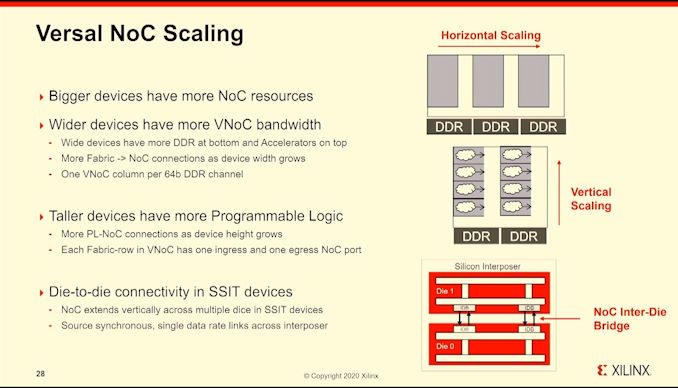

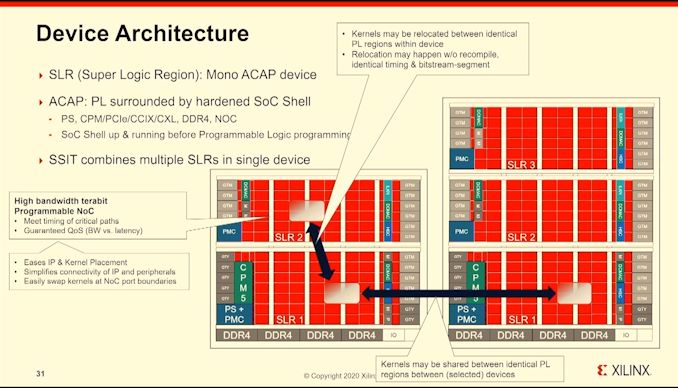

12:20PM EDT - NoC is scalable depending on the Versal product

12:21PM EDT - One VNoC per 64b DDR channel

12:21PM EDT - VNoC can extend with die-to-die connections

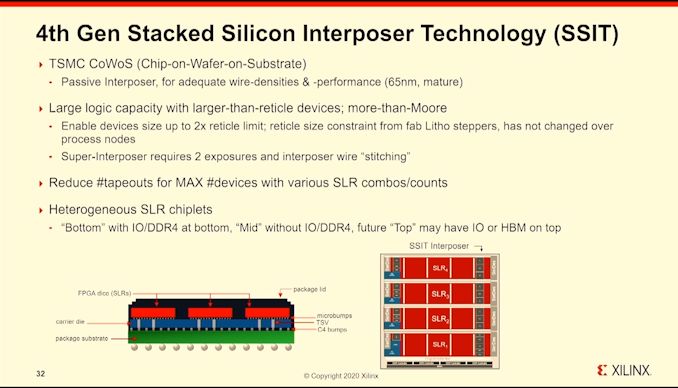

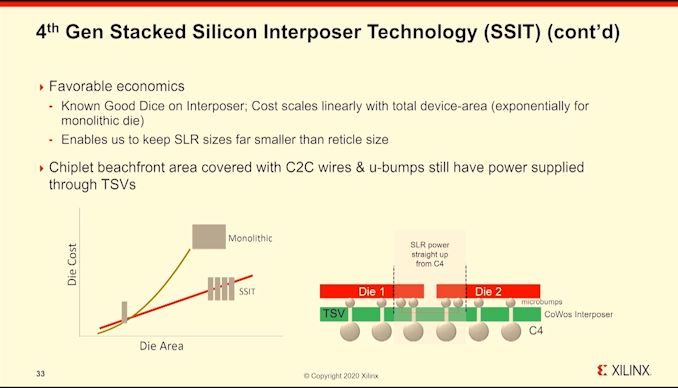

12:22PM EDT - Stacked silicon interposers

12:23PM EDT - 4th Gen Stacked Silicon Interposer, TSMC 7nm CoWoS

12:23PM EDT - Up to 2x reticle limit

12:23PM EDT - Interposer is passive on 65nm

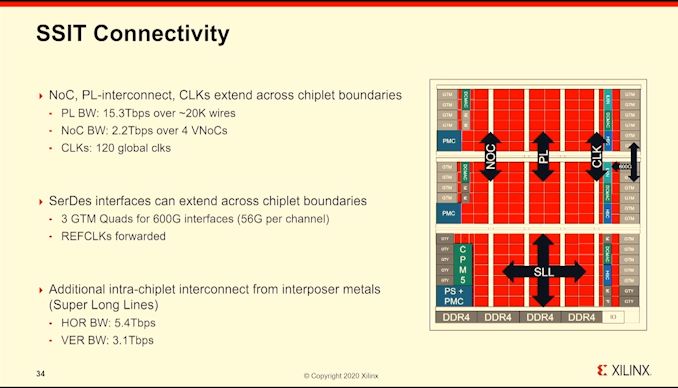

12:24PM EDT - 15.3 Tb/s chip-to-chip bandwidth over 20k wires

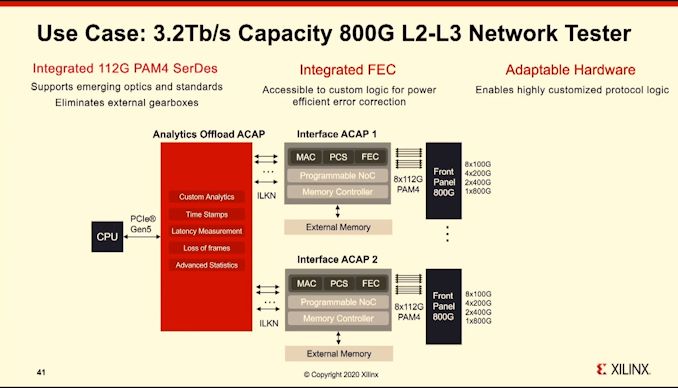

12:25PM EDT - Now use cases

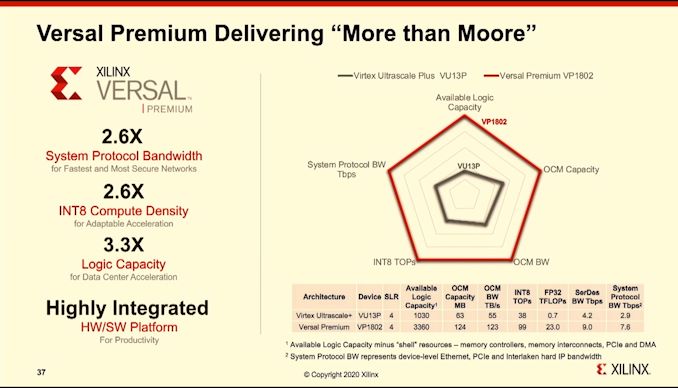

12:26PM EDT - Against Prev Gen Ultrascale+ VU13P

12:29PM EDT - 92B Transistors in Premium

12:30PM EDT - Q&A Time

12:31PM EDT - Q: Latency through NoC Access point? A: NoC is user programmable - can provide QoS and latency requirements on the NoC. The latency that is experienced is dependent on those settings. There's documentation on the NoC for specific scenarios in simulation and design

12:32PM EDT - A: Constraints on PL kernels for recompiles for moved them around? A: Have to place them in programmable logic patterns that are repeated. Similar constraints between devices. Need better documentation

12:33PM EDT - Q: Total die size? 92B? A: No comment on total die area. Applies to largest stacked silicon device

12:34PM EDT - Q: LPDDR5 support? A: No comment.

12:34PM EDT - Q: HBM bandwidth? A: Cannot comment at this point. Keep an eye on future announcements

12:36PM EDT - Q: Can external chiplets attach to NOC? A: Theory yes, but I don't think that any of them exist today

12:37PM EDT - That's a wrap. Next talk for me is the Tofino2 switch chip at 10:30am PT.

1 Comments

View All Comments