AMD: EPYC "Genoa-X" CPUs With 1.1GB of L3 Cache Now Available

by Ryan Smith on June 13, 2023 2:31 PM EST

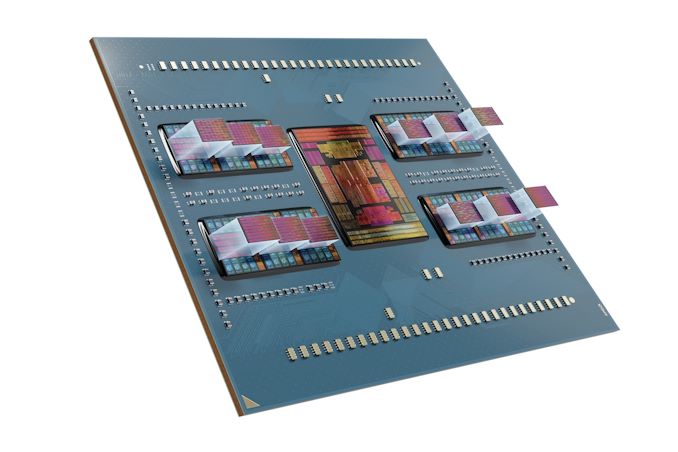

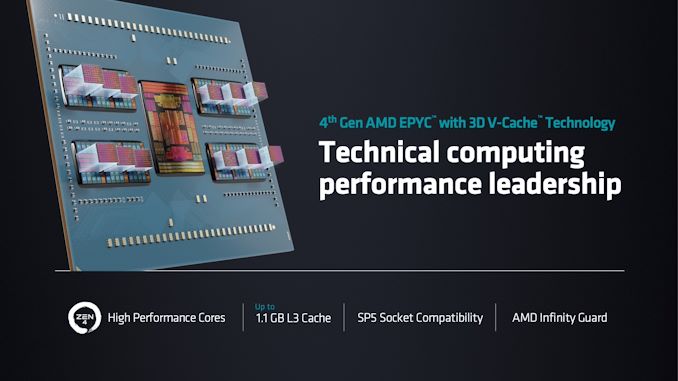

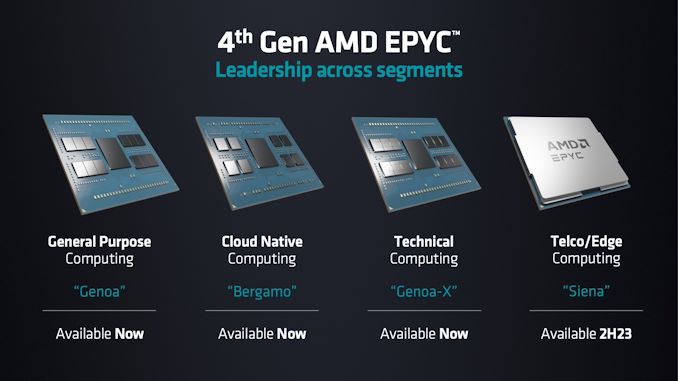

Alongside today’s EPYC 97x4 “Bergamo” announcement, AMD’s other big CPU announcement of the morning is that their large cache capacity “Genoa-X” EPYC processors are shipping now. First revealed by AMD back in June of last year, Genoa-X is AMD’s now obligatory V-cache equipped EPYC server CPU, augmenting the L3 cache capacity of AMD’s core complex dies by stacking a 64MB L3 V-cache die on top of each CCD. With this additional cache, a fully-equipped Genoa-X CPU can offer up to 1152MB of total L3 cache.

Genoa-X is the successor to AMD’s first-generation V-cache part, Milan-X. Like its predecessor, AMD is using cache die stacking to add further L3 cache to otherwise regular Genoa Zen 4 CCDs, giving AMD a novel way to produce a high-cache chip design without having to actually lay out an fab a complete separate die. In this case, with 12 CCDs on a Genoa/Genoa-X chip, this allows AMD to add 768MB of additional L3 cache to the chip.

Like its predecessor, these high-cache SKUs are aimed at a niche market segment of workloads that benefit specifically from the additional cache, which AMD terms their “technical computing” market. To make full use of the additional cache, a workload needs to be cache capacity limited – that is to say, it needs to significantly benefit from having more data available on-chip via the larger L3 cache. This typically only a subset of server/workstation workloads, such as fluid dynamics, databases, and electronic design automation, which is why these high cache chips serve a narrower portion of the market. But, as we saw with Milan-X, in the right situation the performance benefits can be significant.

| AMD EPYC 9084X Genoa-X Processors | |||||||||

| AnandTech | Core/ Thread |

Base Freq |

1T Freq |

L3 Cache |

PCIe | Memory | TDP (W) |

Price (1KU) |

|

| 9684X | 96 | 192 | 2550 | 3700 | 1152MB | 128 x 5.0 | 12 x DDR5-4800 | 400 | $14,756 |

| 9384X | 32 | 64 | 3100 | 3900 | 768MB | 128 x 5.0 | 12 x DDR5-4800 | 320 | $5,529 |

| 9184X | 16 | 32 | 3550 | 4200 | 768MB | 128 x 5.0 | 12 x DDR5-4800 | 320 | $4,928 |

As these are otherwise stock Genoa chips, Genoa-X chips use the same SP5 socket as Genoa and Bergamo. AMD hasn’t disclosed the TDPs, but based on Milan-X, we’re expecting a similar range of TDPs. The additional cache and its placement on top of the CCD means that V-cache equipped CCDs are a bit more power hungry, and the cache die does pose some additional challenges with regards to cooling. So there are some trade-offs involved in performance gains from the extra cache versus performance losses from staying within the SP5 platform’s TDP ranges.

As with Bergamo, we expect to have a bit more on Genoa-X soon. So stay tuned!

7 Comments

View All Comments

Kevin G - Tuesday, June 13, 2023 - link

I was hoping to see a 12 chiplet, 24 core, 1152 MB L3 cache version that was frequency optimized (~4.5 Ghz one thread tubro, ~3.7 Ghz base). Still for those looking for high single threaded performance, the 9184X should fit that niche well, just not going all out.One thing I haven't heard is two DIMM per channel support officially for existing Genoa parts. That was something AMD was in the process of validating this during the Genoa launch with it as a supported feature down the road. Well Genoa just got its first refresh.

duploxxx - Wednesday, June 14, 2023 - link

The Dual dimm support is available, you can find it on several Tyan, Asus and other board vendors... It is the typical OEM that have no offering (SuperMIcro) does have. The usual OEM think they know better and want to controll the market, just like they don't really want to offer the single socket AMD much (yes they have it in portfolio) but OEM mngmnt and marketing don't like it and want to get rid of it. But actually its the best virtualization server you can get (single socket) no numa hassle, good balance memory and io wise. (off course mass people are used to the Intel dual socket habbit) like to sell dual cpu....dontlistentome - Wednesday, June 14, 2023 - link

Presumably Apple will still claim their M2 Ultra Mega Turbo is 5-6x faster than this whilst making you more attractive to all sexes?mikegrok - Wednesday, June 14, 2023 - link

Apple's ram is faster. The primary limitation for latency is the speed of light in copper between the memory and the cpu. Apple places their ram closer, so it has lower latency than memory sockets.back2future - Thursday, June 15, 2023 - link

What's the difference in (arch) priorities, memory access patterns, interconnections, (shared through DMA?), memory cost/size, availability or Kernel support (2023) between V-cache and HBM? (Thx)parrot1553 - Friday, June 16, 2023 - link

I wonder how these will do in gaming! all that L3 cache mmmnandnandnand - Friday, June 16, 2023 - link

Not too great, since it will have lower clocks and the same 96 MB per core as 7800X3D.